Various projects and labs I have worked on during my time in Professor Izidor Gertner's Computer Architecture & Organization class (CS 342 & 343) during the Fall 2019 Semester at the City College of New York

DISLCAIMER: Some of these projects use a 7 Segment Decoder file to output hexadecimal numbers on the Altera board's display. This file was written by classmate Ayushya Amitabh. I do not claim ownership of this file.

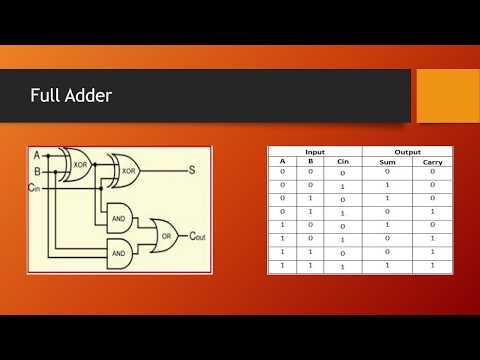

In this lab, I designed a miniature Arithmetic Logic Unit (ALU) using VHDL. The ALU is one of the most crucial components of a CPU and is responsible for performing arithmetic and logic operations. After creating several components in VHDL, I mounted the design onto an Altera DE2 board using Intel's Quartus software. A demo of the design is provided in the video.

This lab's purpose was to simulate Static Random Access Memory (SRAM) using D-latches and Flip-Flops. The components of this project were built using Quartus Block Diagrams. The goal of this lab was to be able to create a simulation of reading and writing into different addresses of memory using an Altera DE2 board. A demo is provided in the video.

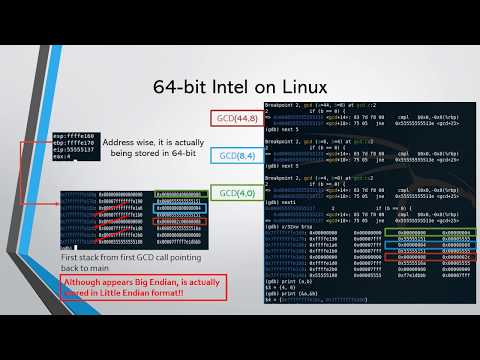

A take home lab to observe how recursive calls are handled in memory across different platforms. I use the Euclidean Greatest Common Divisor (GCD) algorithm for example. The different platforms I look at are MIPS instruction set on a MARS simulator, x86 Intel Processor on Microsoft Visual Studio IDE, and a 64-bit Intel Processor on a Linux platform. My findings are shown in this video.